- 品牌

- 赛芯微xysemi,上海如韵,上海芯龙

- 型号

- 齐全

- 封装形式

- DIP,SOP/SOIC,PLCC,SMD,BGA,TQFP,PQFP,QFP,CSP,TSOP,PGA,QFP/PFP,MCM,SDIP

2串锂保集成MOS船运模式XBM325两串锂电池保护芯片介绍35W以内2串锂保集成MOS内置均衡船运模式:对两节节串联可再充电锂离子/锂聚合物电池的过充电、过放电和过电流进行保护,同时具备电池反接保护功能,这些功能对于锂电池的安全使用极其重要3。过电流保护阈值调节:保护芯片功能基本保护功能:对两节节串联可再充电锂离子/锂聚合物电池的过充电、过放电和过电流进行保护,同时具备电池反接保护功能,这些功能对于锂电池的安全使用极其重要3。过电流保护阈值调节,可组成一个充放电工作的电路。若再加上锂电池输出电路,锂电池就可以实现边充边放的功能芯纳科技经销赛芯微 ic,MOS 管性能稳定,为电源电路提供可靠开关支持。苏州XBM3215JFG赛芯集成MOS 两节锂保

赛芯 XR4981A,在航模动力系统解决方案中表现突出。航空模型对动力系统的重量和效率要求严苛,赛芯 XR4981A 的 QFN3*3-16 封装重量为 2g,比传统控制器轻 30%,降低了航模的整体重量。其高输出功率能为航模电机提供稳定动力,测试显示,搭载该控制器的航模,续航时间延长 8%,飞行姿态更加稳定。在高速飞行时,该控制器的带载能力确保了电机不会出现动力衰减,操控响应灵敏。其宽输入电压范围适配不同规格的锂电池组,在电池电量变化时仍能维持稳定输出,避免了航模空中失控。合作的航模厂商表示,使用该控制器后,航模的故障率降低 15%,飞行安全性提升,为航空模型的性能提升提供了有力支持。

江门DS6036赛芯内置MOS 两节锂保太阳能板供电的锂电池、磷酸铁锂电池充电管理芯片。

二级保护电路设计要点二级保护电路的设计要点主要包括以下几个方面:1.电路组成和工作原理二级保护电路通常包括***级静电保护电路和第二级静电保护电路。***级静电保护电路连接于输入管脚和接地端之间,而第二级静电保护电路则包括电阻和MOS晶体管,其中MOS晶体管的源极和漏极均与输出管脚相连,其栅极与接地端相连,衬体端也与接地端相连。这样的设计可以在减少占用芯片面积的同时,维持相同的静电保护效果3。2.保护电路的选择和应用在设计保护电路时,需要根据具体的应用场景选择合适的保护元件。例如,瞬态电压抑制二极管(TVS)是一种常用的电子元件,用于保护电路免受过电压的影响。在电力系统、通信设备、计算机硬件和其他敏感电子设备中,TVS是不可或缺的保护元件1。3.电路的稳定性和可靠性在设计二级保护电路时,还需要考虑电路的稳定性和可靠性。例如,在激光二极管保护电路的设计中,需要重点分析电流、瞬态电压处理等关键因素。

4串锂电池保护芯片介绍,XBM5574级联功能/集成均衡/NTC/Sense保护芯片功能基本保护功能:对两节节串联可再充电锂离子/锂聚合物电池的过充电、过放电和过电流进行保护,同时具备电池反接保护功能,这些功能对于锂电池的安全使用极其重要。过电流保护阈值调节:4串锂电池的保护芯片电路的过电流保护阈值由开关MOS管决定,如果觉得该阈值较小,可以将多个开关MOS管进行并联操作,以增大过流电流,将两节锂电池保护芯片电路和两节锂电池的充电电路连接在一起,可组成一个充放电工作的电路。若再加上锂电池输出电路,锂电池就可以实现边充边放的功能高耐压理电保护产品、具有低功耗、高过流精度、小封装、无管压降等特点、支持4.2V。

电量计芯 片是一种用于监测和计算锂电池电量的集成电路。其原理通常是通过测量一个特定电阻两端的电压,将电压除以该电阻的阻值得到即时电流值,芯片内集成的取样电阻在流过不同电流时会产生不同压差,芯片对这个电压和时间进行积分,从而得到用户使用时的正确电量,常采用库仑计数法实现这一功能\应用场景随着各类智能移动终端的普及,电量计芯片的应用越发***,除了常见的手机、充电宝、无线耳机充电盒等设备,还包括电动汽车、储能系统等领域。例如,手机需要准确显示电池电量,电动汽车需要精确估算续航里程,这些都离不开电量计芯片。市场趋势目前电子产品往小型化、智能化发展,电量计量功能已被多种协议芯片、电源管理芯片所集成,很多产品出于成本及集成度考虑采用协议芯片中集成的电量计功能进行电量显示。但**的电量计芯片测量效果往往更好芯纳科技主营赛芯微 ic,计算机电源管理芯片,保障计算机稳定运行。佛山6096J9r赛芯内置均衡 内置MOS 2节锂保

多节锂电池保护电路, XBM2138 XBM32XX XBM325X XBM3360。苏州XBM3215JFG赛芯集成MOS 两节锂保

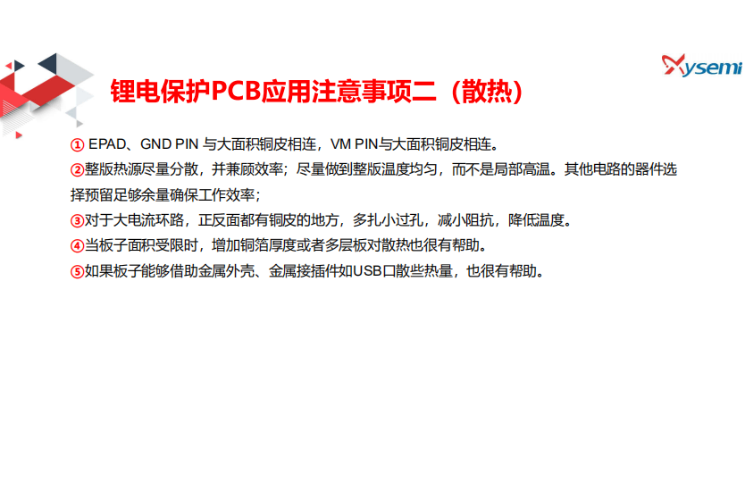

PCBLayout参考---两颗芯片并联两个同型号的锂电保护可以直接并联,实现几乎是直接翻倍的带载能力,降低内阻,提高效率,但布板清注意:①两个芯片尽量对称,直接跨接在B-和大地上。②B-和VM尽量大面积铺地,减小布线内阻和加强散热。③,每片锂电保护IC都需要一个。100Ω电阻**好共用一颗电阻,并且布的离VDD近些,尽量与两个芯片距离差不都。④VDD采样线可以略长些,也无需多粗,但需要绕开干扰源-VDD采样线里面没有大电流。PCBLayout参考---DFN1*1-4①DFN1*1-4封装较小,PCB板上,封装焊盘略大一些,避免虚焊。②,走线经过电阻后,先经过电容再到芯片的VDD。③电容的GND尽量短的回到芯片的GND,使整个电容环路**小。④芯片的GND(B-)到VM建议预留一个C2()电容位置,C2电容可以提高ESD和抗干扰能力。⑤芯片的EPAD,建议连接芯片的GND(B-)或者悬空。苏州XBM3215JFG赛芯集成MOS 两节锂保

PCBLayout参考---两颗芯片并联两个同型号的锂电保护可以直接并联,实现几乎是直接翻倍的带载能力,降低内阻,提高效率,但布板清注意:①两个芯片尽量对称,直接跨接在B-和大地上。②B-和VM尽量大面积铺地,减小布线内阻和加强散热。③,每片锂电保护IC都需要一个。100Ω电阻**好共用一颗电阻,并且布的离VDD近些,尽量与两个芯片距离差不都。④VDD采样线可以略长些,也无需多粗,但需要绕开干扰源-VDD采样线里面没有大电流。PCBLayout参考---DFN1*1-4①DFN1*1-4封装较小,PCB板上,封装焊盘略大一些,避免虚焊。②,走线经过电阻后,先经过电容再到芯片的VDD。③电容的G...

- 无锡XBM5254赛芯现货 2026-04-19

- 深圳2m1EAB赛芯集成MOS 两节锂保 2026-04-19

- 上海XBM5244 赛芯厂家 2026-04-19

- 扬州XBM5770 赛芯厂家 2026-04-19

- 中山6096J9m赛芯集成MOS 两节锂保 2026-04-19

- 东莞2m1EAB赛芯代理 2026-04-19

- 苏州XBM4451赛芯内置MOS 两节锂保 2026-04-19

- 汕头XBM5774 赛芯方案公司 2026-04-19

- 天津XBM3204DBA赛芯现货 2026-04-19

- 韶关DS6066赛芯原厂 2026-04-14

- 中山2m1EAB赛芯厂家 2026-04-14

- 南京3m1FAB赛芯内置MOS 两节锂保 2026-04-14

- 韶关DS3730赛芯代理 2026-04-14

- 惠州2e1EAB赛芯内置MOS 两节锂保 2026-04-14

- 珠海XBM5244 赛芯内置MOS 两节锂保 2026-04-14

- 汕头XBM3212JFG赛芯原厂 2026-04-14

- 中山6096J9m赛芯集成MOS 两节锂保 04-19

- 东莞2m1EAB赛芯代理 04-19

- 苏州XBM4451赛芯内置MOS 两节锂保 04-19

- 汕头XBM5774 赛芯方案公司 04-19

- 天津XBM3204DBA赛芯现货 04-19

- XB5606GJ电源管理IC上海如韵 04-14

- DS6036B 04-14

- 韶关DS6066赛芯原厂 04-14

- 扬州XBM3214DBA赛芯代理 04-14

- 佛山2m1EAB赛芯厂家 04-14