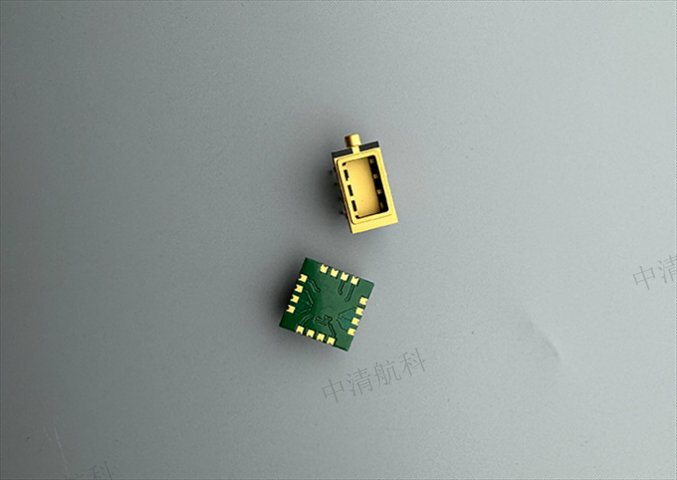

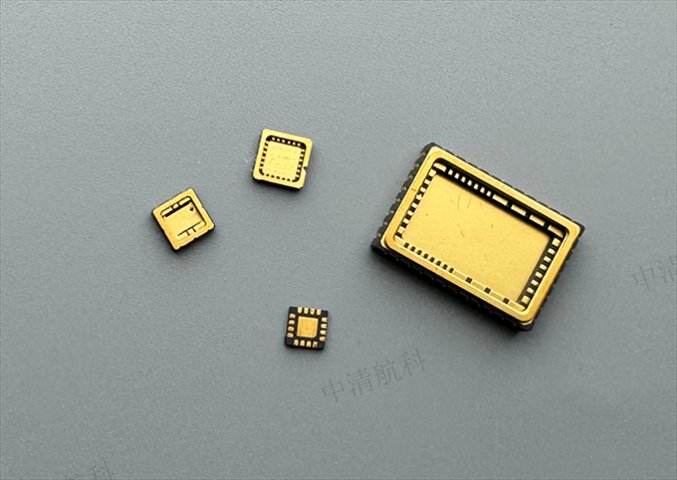

芯片封装的基础概念:芯片封装,简单来说,是安装半导体集成电路芯片的外壳。它承担着安放、固定、密封芯片的重任,能有效保护芯片免受物理损伤以及空气中杂质的腐蚀。同时,芯片封装也是沟通芯片内部与外部电路的关键桥梁,芯片上的接点通过导线连接到封装外壳的引脚上,进而与印制板上的其他器件建立连接。中清航科深谙芯片封装的基础原理,凭借专业的技术团队,能为客户解读芯片封装在整个半导体产业链中的基础地位与关键作用,助力客户从源头理解相关业务。中清航科芯片封装工艺,通过仿真优化,提前规避量产中的潜在问题。上海电子陶瓷封装外壳

面对卫星载荷严苛的空间环境,中清航科开发陶瓷多层共烧(LTCC)MCM封装技术。采用钨铜热沉基底与金锡共晶焊接,实现-196℃~+150℃极端温变下热失配率<3ppm/℃。通过嵌入式微带线设计将信号串扰抑制在-60dB以下,使星载处理器在单粒子翻转(SEU)事件率降低至1E-11errors/bit-day。该方案已通过ECSS-Q-ST-60-13C宇航标准认证,成功应用于低轨卫星星务计算机,模块失效率<50FIT(10亿小时运行故障率)。针对万米级深海探测装备的100MPa超高压环境,中清航科金属-陶瓷复合封装结构。采用氧化锆增韧氧化铝(ZTA)陶瓷环与钛合金壳体真空钎焊,实现漏率<1×10⁻¹⁰Pa·m³/s的密封。内部压力补偿系统使腔体形变<0.05%,保障MEMS传感器在110MPa压力下精度保持±0.1%FS。耐腐蚀镀层通过3000小时盐雾试验,已用于全海深声呐阵列封装,在马里亚纳海沟实现连续500小时无故障探测。上海电子陶瓷封装外壳中清航科专注芯片封装,通过材料革新让微型化与高效能兼得。

中清航科MIL-STD-883认证产线实现金锡共晶焊接工艺。在宇航级FPGA封装中,气密封装漏率<5×10⁻⁸atm·cc/s,耐辐照总剂量达100krad。三防涂层通过96小时盐雾试验,服务12个卫星型号项目。中清航科推出玻璃基板中介层技术,介电常数低至5.2@10GHz。通过TGV玻璃通孔实现光子芯片与电芯片混合集成,耦合损耗<1dB。该平台已用于CPO共封装光学引擎开发,传输功耗降低45%。中清航科建立全维度失效分析实验室。通过3DX-Ray实时监测BGA焊点裂纹,结合声扫显微镜定位分层缺陷。其加速寿命测试模型可精确预测封装产品在高温高湿(85℃/85%RH)条件下的10年失效率。

中清航科WLCSP测试一体化方案缩短生产周期。集成探针卡与临时键合层,实现300mm晶圆单次测试成本降低40%。在PMIC量产中,测试覆盖率达99.2%。面向航天应用,中清航科抗辐照封装通过MIL-STD-750认证。掺铪二氧化硅钝化层使总剂量耐受>300krad,单粒子翻转率<1E-10error/bit-day。已服务低轨卫星星座项目。中清航科MEMS真空封装良率突破98%。采用多孔硅密封技术,腔体真空度维持<0.1Pa十年以上。陀螺仪零偏稳定性达0.5°/h,满足导航级应用。中清航科芯片封装方案,适配边缘计算设备,平衡性能与功耗需求。

面向CPO共封装光学,中清航科开发硅光芯片耦合平台。通过亚微米级主动对准系统,光纤-光栅耦合效率>85%,误码率<1E-12。单引擎集成8通道112GPAM4,功耗降低45%。中清航科微流控生物芯片封装通过ISO13485认证。采用PDMS-玻璃键合技术,实现5μm微通道密封。在PCR检测芯片中,温控精度±0.1℃,扩增效率提升20%。针对GaN器件高频特性,中清航科开发低寄生参数QFN封装。通过金线键合优化将电感降至0.2nH,支持120V/100A器件在6GHz频段工作。电源模块开关损耗减少30%。边缘计算芯片求小求省,中清航科微型封装,适配终端设备空间限制。江苏qfn芯片封装

中清航科芯片封装技术,支持混合信号集成,降低不同电路间的干扰。上海电子陶瓷封装外壳

中清航科的应急响应机制:在生产和服务过程中,难免会遇到突发情况,如设备故障、原材料短缺等。中清航科建立了完善的应急响应机制,能在短时间内启动应急预案,采取有效的应对措施,确保生产和服务不受重大影响。例如,当设备出现故障时,公司的维修团队会迅速到位进行抢修,同时启用备用设备保障生产连续性,比较大限度减少对客户交货周期的影响。芯片封装在新能源领域的应用:新能源领域如新能源汽车、光伏发电等,对芯片的可靠性和耐温性有较高要求。中清航科为新能源汽车的电池管理系统芯片提供高可靠性封装,确保芯片在高低温环境下准确监测和管理电池状态;为光伏发电设备的控制芯片提供耐候性强的封装,保障设备在户外复杂环境下稳定运行,助力新能源产业的发展。上海电子陶瓷封装外壳