先进芯片封装技术 - 2.5D/3D 封装:2.5D 封装技术可将多种类型芯片放入单个封装,通过硅中介层实现信号横向传送,提升封装尺寸和性能,需用到硅通孔(TSV)、重布线层(RDL)、微型凸块等主要技术。3D 封装则是在垂直方向叠放两个以上芯片,直接在芯片上打孔和布线连接上下层芯片堆叠,集成度更高。中清航科在 2.5D/3D 封装技术方面持续创新,已成功应用于高性能计算、人工智能等领域,帮助客户实现芯片性能的跨越式提升。有相关需求欢迎随时联系。芯片封装成本压力大,中清航科材料替代方案,在降本同时保性能。上海射频芯片 sip封装

先进芯片封装技术 - 晶圆级封装(WLP):晶圆级封装是在晶圆上进行封装工艺,实现了芯片尺寸与封装尺寸的接近,减小了封装体积,提高了封装密度。与传统先切割晶圆再封装不同,它是先封装后切割晶圆。中清航科的晶圆级封装技术处于行业前沿,能够为客户提供高集成度、小型化的芯片封装产品,在物联网、可穿戴设备等对芯片尺寸和功耗要求苛刻的领域具有广阔应用前景。想要了解更多内容可以关注我司官网,另外有相关需求欢迎随时联系。江苏qfp芯片封装芯片封装良率影响成本,中清航科工艺改进,将良率提升至行业前列。

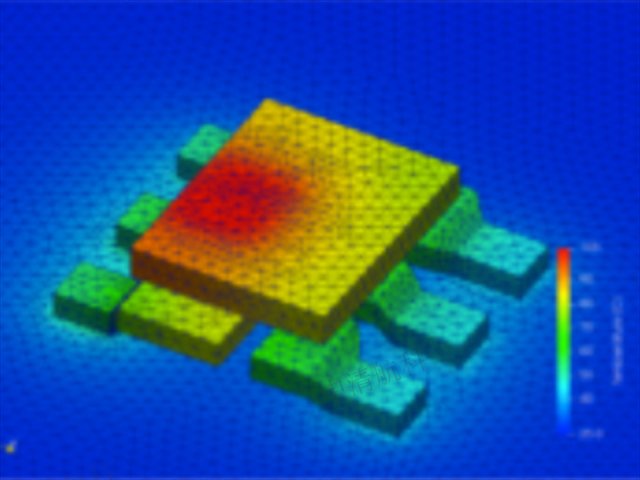

随着摩尔定律逼近物理极限,先进封装成为提升芯片性能的关键路径。中清航科在Fan-Out晶圆级封装(FOWLP)领域实现突破,通过重构晶圆级互连架构,使I/O密度提升40%,助力5G射频模块厚度缩减至0.3mm。其开发的激光解键合技术将良率稳定在99.2%以上,为毫米波通信设备提供可靠封装方案。面对异构集成需求激增,中清航科推出3D SiP立体封装平台。该方案采用TSV硅通孔技术与微凸点键合工艺,实现CPU、HBM内存及AI加速器的垂直堆叠。在数据中心GPU领域,其散热增强型封装结构使热阻降低35%,功率密度提升至8W/mm²,满足超算芯片的严苛要求。

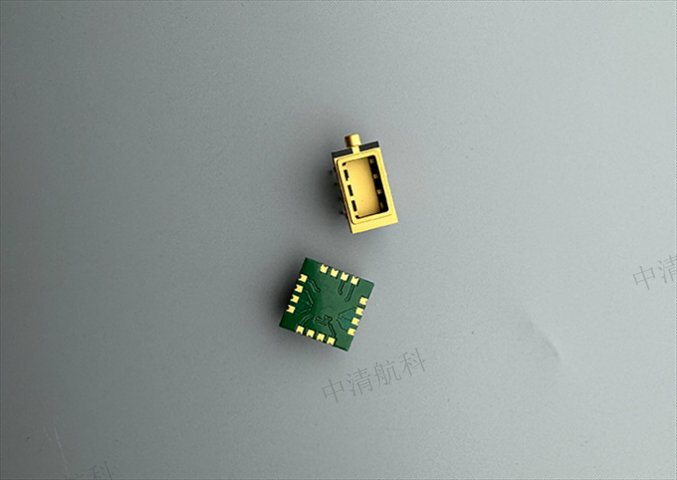

针对5nm芯片200W+热功耗挑战,中清航科开发嵌入式微流道冷却封装。在2.5D封装中介层内蚀刻50μm微通道,采用两相冷却液实现芯片级液冷。实测显示热点温度降低48℃,同时节省80%外部散热空间,为AI服务器提供颠覆性散热方案。基于低温共烧陶瓷(LTCC)技术,中清航科推出毫米波天线集成封装。将24GHz雷达天线阵列直接封装于芯片表面,信号传输距离缩短至0.2mm,插损低于0.5dB。该方案使77GHz车规雷达模块尺寸缩小60%,量产良率突破95%行业瓶颈。中清航科芯片封装方案,适配物联网设备,兼顾低功耗与小型化。

中清航科的客户服务体系:质优的客户服务是企业赢得客户信任的重要保障。中清航科建立了完善的客户服务体系,从前期的技术咨询、方案设计,到中期的生产跟进、质量反馈,再到后期的售后服务、技术支持,为客户提供全流程、一站式的服务。公司设有专门的客户服务团队,及时响应客户需求,解决客户问题。通过定期回访客户,了解产品使用情况,收集客户建议,不断优化产品和服务,与客户建立长期稳定的合作关系。想要了解更多内容可以关注我司官网,同时欢迎新老客户来电咨询。中清航科芯片封装工艺,通过仿真优化,提前规避量产中的潜在问题。浙江江苏半导体封装公司

中清航科芯片封装技术,平衡电气性能与机械保护,延长芯片使用寿命。上海射频芯片 sip封装

中清航科超细间距倒装焊工艺突破10μm极限。采用激光辅助自对准技术,使30μm微凸点对位精度达±1μm。在CIS图像传感器封装中,该技术消除微透镜偏移问题,提升低光照下15%成像质量。中清航科开发出超薄中心less基板,厚度100μm。通过半加成法(mSAP)实现2μm线宽/间距,传输损耗低于0.3dB/mm@56GHz。其5G毫米波AiP天线封装方案已通过CTIA OTA认证,辐射效率达72%。为响应欧盟RoHS 2.0标准,中清航科推出无铅高可靠性封装方案。采用Sn-Bi-Ag合金凸点,熔点138℃且抗跌落性能提升3倍。其绿色电镀工艺使废水重金属含量降低99%,获三星Eco-Partner认证。上海射频芯片 sip封装

中清航科(江苏)科技有限公司是一家有着先进的发展理念,先进的管理经验,在发展过程中不断完善自己,要求自己,不断创新,时刻准备着迎接更多挑战的活力公司,在江苏省等地区的数码、电脑中汇聚了大量的人脉以及**,在业界也收获了很多良好的评价,这些都源自于自身的努力和大家共同进步的结果,这些评价对我们而言是比较好的前进动力,也促使我们在以后的道路上保持奋发图强、一往无前的进取创新精神,努力把公司发展战略推向一个新高度,在全体员工共同努力之下,全力拼搏将共同中清航科科技供应和您一起携手走向更好的未来,创造更有价值的产品,我们将以更好的状态,更认真的态度,更饱满的精力去创造,去拼搏,去努力,让我们一起更好更快的成长!