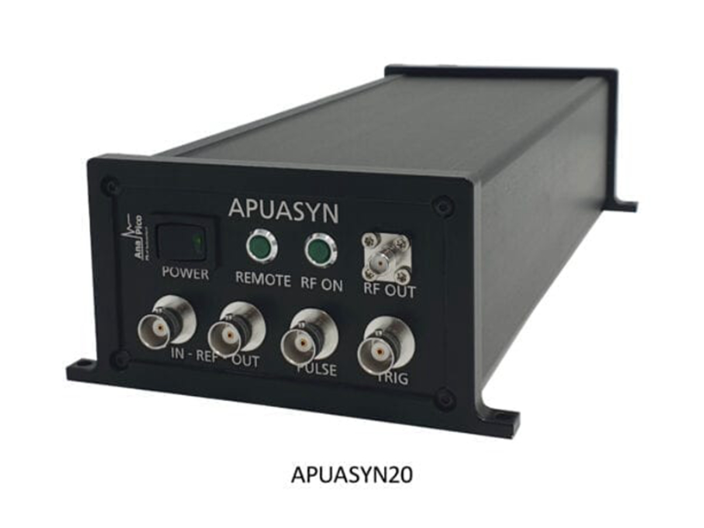

本振频率调节范围取决于分频系数的变化范围,准确地说,取决于分频器的位数,由于位数是任意的(理论上),所以频率调节范围相当宽,也就是可预选的电视频道相当多。频率合成式高频头能兼容接收CATV有线增补频道,不过,要在CPU的控制数据中增加CATV增补频道所需的频道数据才行。这些必须要在CPU的软件设计中由生产厂家事先设定,一般用户及检修人员无法改变。频率合成技术还广泛应用于手机的发射电路、本振电路中,这里不再具体分析,有兴趣的读者可参考相关书籍。AnaPico宽带频率综合器输出范围分别覆盖8kHz至20GHz、22GHz和40GHz,分辨率低至0.00001Hz。天津频率综合器销售

传统上综合器是为了在其工作频率范围内产生一个连续信号。其振幅在一定范围内随频率变化。然而,较新的设计带来更多的如振幅均衡和控制功能。输出电平可以采用开环控制(查表)或更复杂的闭环自动电平控制(ALC)方案来校准和控制。此外,现在工业界需要更复杂的包括传统的模拟调制(幅度、频率、相位和脉冲)到复杂的矢量形式,如IQ调制的波形。这些调制功能连同振幅控制和谐波抑制现在不仅可以制作成笨重的测试和测量信号发生器,也可以制作成较小的模块形式。主要性能特点(如相位噪声、杂散和切换速度)正在逐步接近那些测试和测量信号发生器。江苏简单易操作频率综合器市场报价在精密测量和科学研究领域中,频率综合器可用于提供高稳定性和低抖动的参考信号。

频率源是无线通信系统的重要硬件组成部分,它为射频收发系统提供本地振荡信号来完成上下变频功能,是各类型号产品中不可缺少的重要部件,而频率综合器则是实现可编程频率源的重要器件。面对弹载设备升级换代、提升竞争力的迫切需求,传统的频率源设计方式面临减体积、降成本的巨大压力。因此,研发拥有自主知识产权的宽带PLL频率综合器芯片,不仅能够有效促进系统体积减小、成本降低,也能够为系统的硬件可重构提供器件基础,更有助于实现重要技术的自主可控,对于武器系统中射频收发的微小型化设计乃至整机SoC设计的作用和意义都非常大。

频率源作为雷达、通信和导航等电子系统中关键部件之一,其性能直接影响电子系统的整体性能。随着电子信息领域的快速发展,各种通信系统对于频率源的性能指标需求更高。低相噪、高频率、宽带宽、高功率、低杂散、捷变频、小步进和小型化是频率源设计的理想化目标。为了实现便携式W波段固态测云雷达,本文根据该雷达需求设计了一款小型化X波段低相噪低杂散的频率源,作为该雷达的“心脏”。首先,研究了目前国内外对X波段及其他其他波段频率源的研究现状和发展情况,对频率源的功能应用进行了简要分析。并研究了频率合成的各种实现方式、频率源主要性能指标及其对雷达系统的影响,详细分析了其中的关键部分及各种实现方式优缺点。其次,结合频率源应用背景及指标要求,重点分析了DS、DDS及PLL这三种方法相混合的结构及各自的优缺点。确定了使用DDS激励PLL的方案来实现小型化、宽带、低相噪、低杂散的频率源,并对整体设计方案进行了结构、芯片、相噪和杂散的可行性论证。 AnaPico频率综合器输出范围覆盖8kHz至40GHz。

频率合成中影响转换速率的因素:频率合成中影响转换速率的因素:1.频率控制锁相环(PPL)常用来提高频率稳定度并使微波信号源的相位噪声达到比较好。通过锁相到一个稳定的参考源-------通常是在较低2.间接合成技术“间接合成”一词通常应用于将输出频率的样本与从参考标准得到的频率作比较并反馈以形成锁相环的方法。输出频率样本可以以频率相除或相乘的方式。频谱纯度是频域指标。理想的正弦信号的频谱只一根谱线,(2)短期频率稳定度和瞬时频率稳定度这是时域指标。短期频率稳定度:从秒级到一天的时间间隔内的频率不稳定性。瞬时频率稳定度:从毫秒到秒量级的时间间隔内的频率不稳定性**常用的时域指标—阿仑方差。频率综合器模块可以将不同频率的参考信号合成为特定频率的射频信号。天津频率综合器销售

频率综合器模块通常用于无线电、通信、雷达、卫星导航、测试测量等领域中。天津频率综合器销售

虽然DDS工作频点接近直流,但根据奈奎斯特原理,其比较高频率只能到时钟频率的一半。虽然可以工作在高于奈奎斯特区,但是性能下降非常快。另一个严重的问题是由于DDS技术中固有的许多因素导致的较高杂散,例如数位截取、量化和DAC转换误差。DSS的形式可以是完全集成的芯片或可以使用单独的现场可编程门阵列(FPGA)和DAC芯片来实现。后者可将数字部分限制在FPGA内部,因此隔离了EMI引起的杂散。如今FPGA有足够的能力来建立相当复杂的多核相位累加器和索引表,由数位截取导致的杂散电平可忽略不计。结果主要的杂散源通常是由于DAC的非线性和量化噪声引起的。天津频率综合器销售